## Diagram: Neural Network to Hardware Implementation Pipeline

### Overview

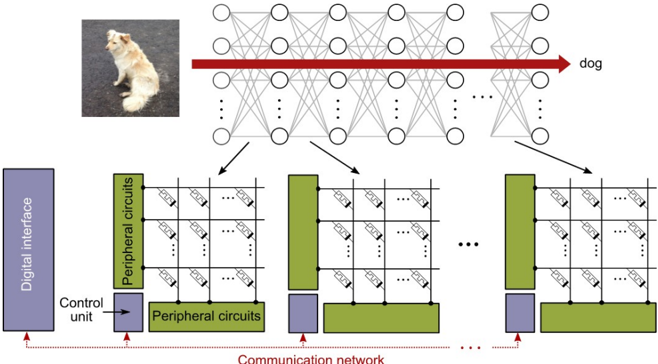

The image is a two-part technical diagram illustrating the conceptual pipeline from image recognition using a neural network to its potential implementation in a modular hardware architecture. The top section depicts a feedforward neural network processing an image of a dog, while the bottom section shows a corresponding hardware block diagram with interconnected processing units.

### Components/Axes

**Top Section (Neural Network):**

* **Input:** A photograph of a small, light-colored dog (likely a puppy) sitting on a dark surface.

* **Network Structure:** A multi-layer, fully connected feedforward neural network. It consists of:

* An input layer (leftmost column of circles).

* Multiple hidden layers (intermediate columns of circles).

* An output layer (rightmost column of circles).

* Connections (lines) between all nodes in adjacent layers.

* **Output Label:** The word "dog" is positioned to the right of the output layer, indicating the network's classification result.

* **Flow Indicator:** A large, solid red arrow points from the input image, through the network, to the output label "dog," signifying the forward propagation of data.

**Bottom Section (Hardware Architecture):**

* **Primary Components (Labeled):**

* **Digital interface:** A large, vertical purple rectangle on the far left.

* **Control unit:** A smaller, square purple block connected to the Digital interface.

* **Peripheral circuits:** A large, green rectangular block connected to the Control unit.

* **Structure:** The diagram shows a repeating modular pattern. Three complete modules are visible, with ellipses (`...`) indicating more modules to the right.

* Each module consists of a **Control unit** (purple square) and a **Peripheral circuits** block (green rectangle).

* Within each "Peripheral circuits" block is a grid of smaller, identical sub-circuits (depicted as small squares with internal diagonal lines and dots).

* **Interconnections:**

* Arrows point from the neural network layers above down to the corresponding hardware modules below, suggesting a mapping of network layers to hardware blocks.

* A red, dashed line labeled **"Communication network"** runs along the bottom, connecting all the hardware modules in a bus-like topology.

* Solid black lines connect the "Control unit" to its associated "Peripheral circuits" within each module.

### Detailed Analysis

**Neural Network Flow:**

1. The process begins with the input image (the dog).

2. Data flows through the network layers, as indicated by the red arrow.

3. The network's final output is the classification label "dog."

**Hardware Mapping:**

1. The diagram proposes a direct, layer-wise or block-wise mapping from the abstract neural network to physical hardware.

2. The "Digital interface" likely serves as the main input/output gateway for the system.

3. The "Control unit" in each module presumably manages the operations for its associated "Peripheral circuits."

4. The "Peripheral circuits" contain the actual processing elements (the grid of sub-circuits) that perform the computations for a segment of the neural network.

5. The "Communication network" facilitates data transfer between the different hardware modules, enabling the distributed processing required for the full network.

### Key Observations

* **Conceptual, Not Quantitative:** This is a high-level architectural diagram. It contains no numerical data, specific performance metrics, or detailed circuit schematics.

* **Modularity and Scalability:** The use of repeating modules with ellipses (`...`) strongly emphasizes a scalable design. More modules can be added to handle larger or more complex neural networks.

* **Abstraction Levels:** The diagram bridges two levels of abstraction: the algorithmic level (neural network) and the hardware implementation level (circuit blocks).

* **Visual Metaphor:** The grid within "Peripheral circuits" is a symbolic representation of parallel processing units, not a literal circuit diagram.

### Interpretation

This diagram serves as a conceptual blueprint for deploying neural networks on specialized hardware, such as a neuromorphic chip or an AI accelerator. It visually argues for a modular, distributed hardware architecture where different parts of the neural network are mapped to dedicated processing blocks.

The key insight is the **separation of concerns**: the "Control unit" handles management and sequencing, while the "Peripheral circuits" handle the bulk of the parallel computation. The "Communication network" is critical, as its bandwidth and latency would be major determinants of the system's overall performance, representing the physical manifestation of the connections between neurons in the software model.

The diagram implies that the complexity of the neural network (top) is directly reflected in the required scale of the hardware (bottom). The "Digital interface" is the bridge to the outside world, where raw data (like the dog image) enters and final results (like the "dog" label) are output. This is a foundational concept in edge AI and dedicated AI hardware design, aiming for efficiency and speed by moving computation away from general-purpose CPUs.