\n

## Pie Chart: Component Distribution (Likely Hardware/Architecture)

### Overview

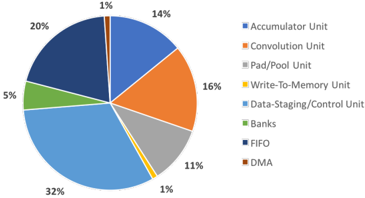

The image displays a pie chart illustrating the percentage distribution of various functional units or components within a system, likely related to computer architecture, memory hierarchy, or hardware design. The chart is accompanied by a color-coded legend on the right.

### Components/Axes

* **Chart Type:** Pie Chart.

* **Legend:** Positioned on the right side of the image, vertically aligned. It lists 8 categories with corresponding color squares.

* **Data Labels:** Percentage values are placed directly adjacent to their corresponding pie segments.

* **Categories (from Legend):**

1. Accumulator Unit (Medium Blue)

2. Convolution Unit (Orange)

3. Pad/Pool Unit (Gray)

4. Write-To-Memory Unit (Yellow)

5. Data-Staging/Control Unit (Light Blue)

6. Banks (Green)

7. FIFO (Dark Blue)

8. DMA (Darker Blue/Indigo)

### Detailed Analysis

The pie chart is divided into eight segments. The following lists each segment, its approximate percentage, color, and spatial position within the pie (starting from the top and moving clockwise):

1. **DMA:** ~1%. Color: Darker Blue/Indigo. Position: A very thin slice at the top (12 o'clock position).

2. **Accumulator Unit:** ~14%. Color: Medium Blue. Position: Upper-right quadrant.

3. **Convolution Unit:** ~16%. Color: Orange. Position: Right side, below the Accumulator Unit segment.

4. **Pad/Pool Unit:** ~11%. Color: Gray. Position: Lower-right quadrant.

5. **Write-To-Memory Unit:** ~1%. Color: Yellow. Position: A very thin slice at the bottom (6 o'clock position).

6. **Data-Staging/Control Unit:** ~32%. Color: Light Blue. Position: Large segment occupying the lower-left quadrant and extending upward on the left side. This is the largest segment.

7. **Banks:** ~5%. Color: Green. Position: Left side, above the Data-Staging/Control Unit segment.

8. **FIFO:** ~20%. Color: Dark Blue. Position: Upper-left quadrant. This is the second-largest segment.

**Cross-Reference Verification:** The colors of the segments in the pie chart correspond directly to the color squares next to each label in the legend on the right. The two smallest segments (DMA and Write-To-Memory Unit) are both 1% and are represented by distinct, thin slices at the top and bottom of the chart, respectively.

### Key Observations

* **Dominant Components:** The **Data-Staging/Control Unit (32%)** and **FIFO (20%)** together account for over half (52%) of the total distribution, indicating these are the most significant components by the measured metric (e.g., area, power, complexity).

* **Secondary Components:** The **Convolution Unit (16%)**, **Accumulator Unit (14%)**, and **Pad/Pool Unit (11%)** form a middle tier, each representing a substantial portion.

* **Minor Components:** **Banks (5%)**, **Write-To-Memory Unit (1%)**, and **DMA (1%)** constitute a small fraction of the total.

* **Distribution Shape:** The distribution is highly uneven, with a long tail of smaller components following a few large ones.

### Interpretation

This chart likely represents the resource allocation (e.g., silicon area, power budget, or design complexity) across different functional blocks in a specialized computing unit, such as a neural processing unit (NPU), tensor core, or memory controller. The naming of units like "Convolution," "Pad/Pool," "Accumulator," and "FIFO" strongly suggests a context of machine learning acceleration or dataflow processing.

The data suggests that **data movement, buffering, and control (Data-Staging/Control Unit and FIFO)** are the primary consumers of resources, which is a common characteristic in data-intensive architectures where managing data flow is critical. The significant allocation to the **Convolution Unit** aligns with its role as a fundamental compute operation in convolutional neural networks. The very small allocations for **DMA** and **Write-To-Memory** might indicate these are either highly optimized, fixed-function blocks or that the chart measures a specific aspect (like active compute area) where these units are less prominent. The "Banks" likely refer to memory banks, and their 5% share suggests on-chip memory is a notable but not dominant resource in this breakdown.

**Note:** The exact metric (area, power, etc.) is not specified in the image. The interpretation is inferred from the component names and typical architectural trade-offs.