```markdown

## Diagram: System Architecture with Data Flow and Timing Labels

### Overview

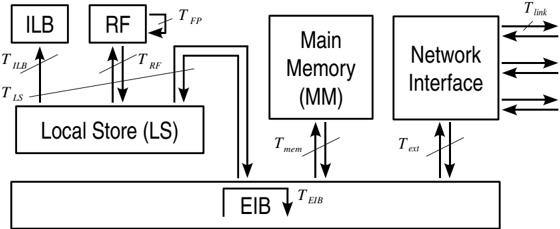

This diagram illustrates a system architecture with multiple components connected by labeled arrows representing data flow and timing delays. Key elements include the Input/Load Buffer (ILB), Request FIFO (RF), Local Store (LS), Main Memory (MM), Network Interface, and External Interface Buffer (EIB). Arrows indicate bidirectional data paths with associated time labels (e.g., T_ILB, T_mem).

### Components/Axes

- **Components**:

- ILB (Input/Load Buffer)

- RF (Request FIFO)

- LS (Local Store)

- MM (Main Memory)

- Network Interface

- EIB (External Interface Buffer)

- **Arrows/Labels**:

- **T_ILB**: Data flow from ILB to LS (upward arrow).

- **T_LS**: Data flow from LS to ILB (downward arrow).

- **T_RF**: Data flow from RF to LS (downward arrow).

- **T_FP**: Data flow from RF to FP (rightward arrow).

- **T_mem**: Data flow between LS and MM (downward arrow).

- **T_ext**: Data flow from Network Interface to MM (downward arrow).

- **T_link**: Data flow between Network Interface and external systems (horizontal arrows).

- **T_EIB**: Data flow from EIB to LS (downward arrow).

### Detailed Analysis

1. **ILB and RF**:

- ILB and RF are positioned at the top-left, feeding data into LS.

- T_ILB and T_LS indicate bidirectional communication between ILB and LS.

- T_RF shows unidirectional flow from RF to LS.

2. **Local Store (LS)**:

- Central component connected to ILB, RF, MM, and EIB.

- T_mem represents data transfer to/from MM.

3. **Main Memory (MM)**:

- Connected to LS (T_mem) and Network Interface (T_ext).

- T_ext suggests external data access via MM.

4. **Network Interface**:

- Rightmost component with bidirectional T_link arrows, indicating external communication.

- T_ext links MM to Network Interface.

5. **EIB**:

- Bottom component connected to LS (T_EIB) and MM (T_mem).

- Acts as a bridge between LS and external systems.

### Key Observations

- **Bidirectional Flow**: ILB and LS have reciprocal data paths (T_ILB/T_LS).

- **Central Role of LS**: LS is the hub for data exchange between ILB, RF, MM, and EIB.

- **External Communication**: Network Interface handles external data via T_link and T_ext.

- **Timing Hierarchy**: T_mem (LS-MM) and T_EIB (LS-EIB) suggest memory access is faster than external transfers.

### Interpretation

This diagram models a hierarchical system where:

1. **Data originates** from ILB/RF, processed in LS, and stored in MM.

2. **External data** enters via Network Interface, routed through MM to LS/EIB.

3. **Timing constraints** (e.g., T_mem < T_link) imply prioritization of internal memory access over external communication.

4. **EIB** serves as a critical intermediary for external data integration.

The architecture emphasizes minimizing latency in core operations (LS-MM) while managing external delays (