## Diagram: Architecture for a p-computer and 1-bit RNG

### Overview

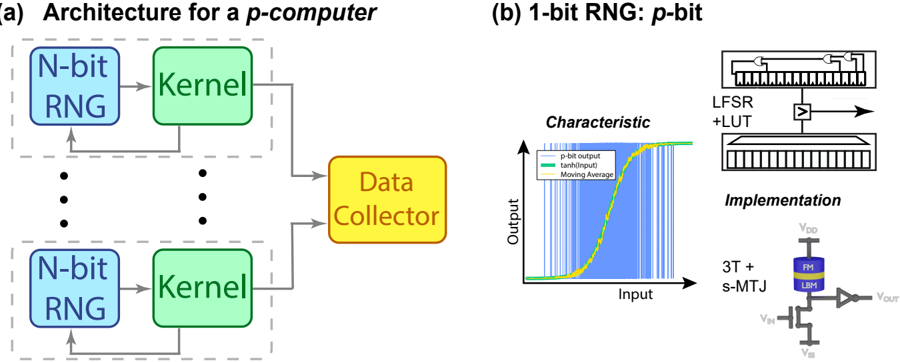

The image presents two diagrams: (a) an architectural overview of a p-computer, and (b) a detailed view of a 1-bit RNG (Random Number Generator) with its characteristic curve and implementation. The diagrams illustrate the components and flow of data within these systems.

### Components/Axes

**Diagram (a): Architecture for a p-computer**

* **Components:** N-bit RNG, Kernel, Data Collector.

* **Connections:** Dotted lines indicate connections between N-bit RNGs and Kernels, and between Kernels and the Data Collector. Solid lines indicate connections between the Data Collector and the Kernels.

* **Labels:** "Architecture for a p-computer", "N-bit RNG", "Kernel", "Data Collector".

**Diagram (b): 1-bit RNG: p-bit**

* **Components:** LFSR + LUT, Characteristic Curve (plot), Implementation (circuit diagram with 3T + s-MTJ, PM, LBM, NM).

* **Axes (Characteristic Curve):**

* X-axis: "Input"

* Y-axis: "Output"

* **Legend (Characteristic Curve):**

* Blue Line: "p-bit output"

* Green Line: "tanh(Input)"

* Light Blue Shaded Area: "Moving Average"

* **Labels:** "1-bit RNG: p-bit", "Characteristic", "Implementation", "Vdd", "Vout", "Vin", "Vss".

### Detailed Analysis or Content Details

**Diagram (a): Architecture for a p-computer**

The diagram shows a parallel architecture. Multiple "N-bit RNG" blocks are connected to "Kernel" blocks. Each Kernel is then connected to a central "Data Collector". The dotted lines suggest a many-to-one connection from RNGs to Kernels, and from Kernels to the Data Collector. The solid lines from the Data Collector to the Kernels suggest a feedback or control mechanism. The number of N-bit RNGs and Kernels is not explicitly stated, but there are at least two of each visible.

**Diagram (b): 1-bit RNG: p-bit**

* **LFSR + LUT:** A block diagram representing a Linear Feedback Shift Register combined with a Look-Up Table. An arrow indicates data flow from left to right.

* **Characteristic Curve:** The curve shows the relationship between Input and Output.

* The "p-bit output" (blue line) starts near 0 for low input values, then rapidly transitions to 1 as the input increases. The transition appears to occur around an input value of approximately 0.5.

* The "tanh(Input)" (green line) is a sigmoid function, starting at approximately -1 for low input values and approaching 1 as the input increases. It crosses 0 at an input value of approximately 0.

* The "Moving Average" (light blue shaded area) represents a smoothed version of the p-bit output, showing a gradual transition from 0 to 1.

* **Implementation:** The circuit diagram shows a 3T + s-MTJ (Spin-Transfer Torque Magnetic Tunnel Junction) configuration with PM (P-channel MOSFET) and LBM (likely a Load Block MOSFET). The circuit is powered by Vdd and grounded by Vss. Vin is the input voltage, and Vout is the output voltage.

### Key Observations

* The p-computer architecture (a) emphasizes parallelism, utilizing multiple RNGs and Kernels.

* The 1-bit RNG (b) utilizes a non-linear characteristic curve (tanh) and a moving average to generate random bits.

* The implementation of the 1-bit RNG (b) uses a 3T + s-MTJ circuit, suggesting a hardware-based implementation.

* The characteristic curve shows a clear threshold effect, where the output switches from 0 to 1 within a narrow range of input values.

### Interpretation

The diagrams illustrate a system for generating random numbers. The p-computer architecture (a) suggests a parallel processing approach to enhance the speed and efficiency of random number generation. The 1-bit RNG (b) provides a detailed view of a specific implementation, utilizing a non-linear function and a hardware circuit to produce random bits. The tanh function and moving average likely contribute to the randomness and statistical properties of the generated bits. The use of an s-MTJ suggests a potential application in secure random number generation, as these devices are sensitive to physical noise. The feedback loop in diagram (a) could be used for error correction or to improve the quality of the random numbers. The overall system appears to be designed for high-performance and potentially secure random number generation.