## System Architecture Diagrams

### Overview

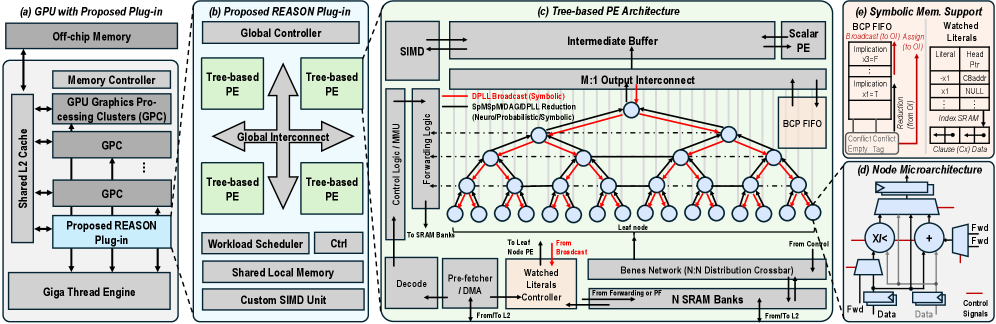

The image presents a set of diagrams illustrating the architecture and components of a system incorporating a "Proposed REASON Plug-in." It includes diagrams of a GPU with the plug-in, the plug-in itself, a tree-based processing element (PE) architecture, a node microarchitecture, and symbolic memory support.

### Components/Axes

* **(a) GPU with Proposed Plug-in:**

* **Components:** Off-chip Memory, Memory Controller, GPU Graphics Processing Clusters (GPC), Shared L2 Cache, Proposed REASON Plug-in, Giga Thread Engine.

* **Flow:** Arrows indicate data flow between components.

* **(b) Proposed REASON Plug-in:**

* **Components:** Global Controller, Tree-based PE (x4), Global Interconnect, Workload Scheduler, Ctrl, Shared Local Memory, Custom SIMD Unit.

* **Flow:** Arrows indicate data flow between components. The Global Interconnect has arrows pointing in all four cardinal directions.

* **(c) Tree-based PE Architecture:**

* **Components:** Intermediate Buffer, M:1 Output Interconnect, Tree structure with nodes, Leaf node, Control Logic/MMU, Forwarding Logic, Decode, Pre-fetcher/DMA, Watched Literals Controller, Benes Network (N:N Distribution Crossbar), N SRAM Banks.

* **Data Flow:**

* DPLL Broadcast (Symbolic) and SpMSPM/DAG/DPLL Reduction (Neuro/Probabilistic/Symbolic) flow through the tree structure.

* Red arrows indicate "From Broadcast".

* Black arrows indicate other data flow.

* "To Leaf Node PE" and "From Broadcast" are indicated at the bottom.

* "From/To L2" is indicated at the bottom.

* **(d) Node Microarchitecture:**

* **Components:** Logic gates, adders, multiplexers, Fwd, Data, Control Signals.

* **Flow:** Arrows indicate data flow and control signals.

* **(e) Symbolic Mem. Support:**

* **Components:** BCP FIFO, Watched Literals, Index SRAM, Clause (Cx) Data.

* **BCP FIFO:** Shows "Broadcast (to Ol) Assign (to Ol)" and "Reduction (from Ol)".

* **Watched Literals:** Table with columns "Literal" and "Head Ptr". Example entries: "-x1" with "C8addr", "x1" with "NULL".

### Detailed Analysis or Content Details

* **GPU with Proposed Plug-in:**

* The Proposed REASON Plug-in is positioned between the GPC and the Giga Thread Engine.

* The Shared L2 Cache connects to the Memory Controller and the GPCs.

* **Proposed REASON Plug-in:**

* The Global Controller is connected to four Tree-based PEs via the Global Interconnect.

* The Workload Scheduler and Ctrl are connected to the Shared Local Memory and Custom SIMD Unit.

* **Tree-based PE Architecture:**

* The tree structure has multiple layers of nodes, culminating in the Leaf nodes.

* The M:1 Output Interconnect connects the top node to the Intermediate Buffer.

* The Watched Literals Controller is connected to the N SRAM Banks via the Benes Network.

* **Node Microarchitecture:**

* The diagram shows a detailed view of a node, including logic gates, adders, and multiplexers.

* "XI<" is a key component.

* **Symbolic Mem. Support:**

* The BCP FIFO handles broadcast and reduction operations.

* The Watched Literals table stores literal and head pointer information.

* The Index SRAM and Clause (Cx) Data are used for clause data storage.

### Key Observations

* The Proposed REASON Plug-in is designed to integrate with a GPU architecture.

* The Tree-based PE Architecture is a key component of the plug-in.

* Symbolic memory support is provided through the BCP FIFO and Watched Literals.

* The Node Microarchitecture provides a detailed view of the processing elements.

### Interpretation

The diagrams illustrate a complex system architecture designed for specialized processing, likely related to symbolic computation or reasoning. The Proposed REASON Plug-in appears to be an accelerator designed to enhance the capabilities of a GPU. The tree-based architecture suggests a hierarchical processing approach, while the symbolic memory support indicates the system's ability to handle symbolic data. The node microarchitecture provides insight into the low-level operations performed by the processing elements. The integration of these components suggests a system optimized for tasks requiring both parallel processing and symbolic reasoning.