## Pipeline Diagram: GPU-REASON and Intra-REASON Pipelines with DPLL-lookahead CDCL

### Overview

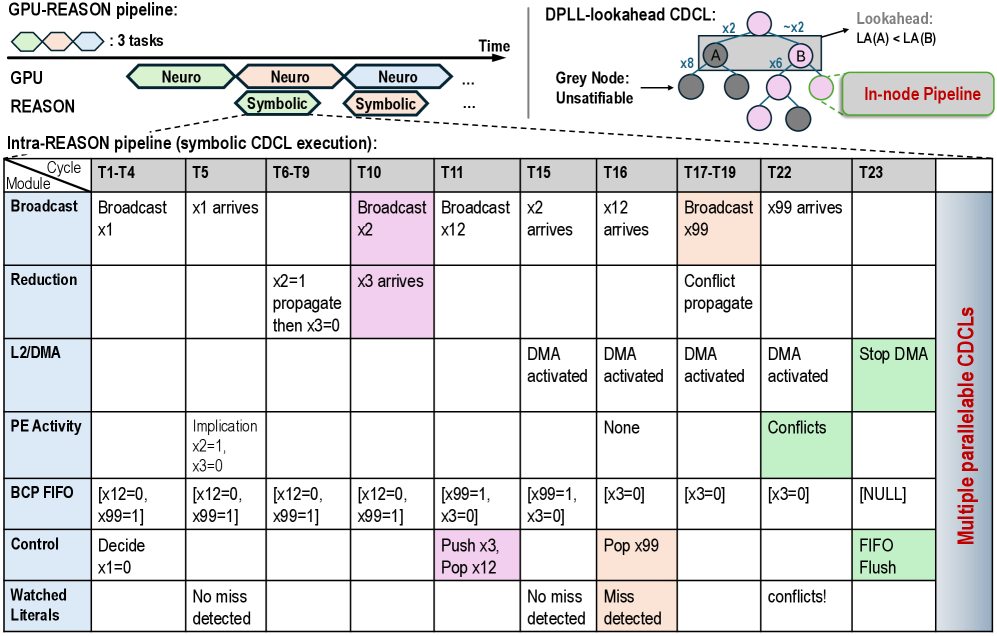

The image presents a diagram illustrating the GPU-REASON pipeline, a DPLL-lookahead CDCL (Conflict-Driven Clause Learning) structure, and an Intra-REASON pipeline focusing on symbolic CDCL execution. It details the flow of tasks and data through different modules and cycles.

### Components/Axes

* **GPU-REASON pipeline:**

* Legend: A sequence of diamond shapes, where each diamond represents a task. The legend indicates that three tasks are shown.

* Pipeline stages: GPU (Neuro), REASON (Symbolic). The pipeline shows alternating Neuro and Symbolic processing stages.

* Axis: Time (horizontal axis).

* **DPLL-lookahead CDCL:**

* Nodes: Represented as circles, some filled in grey (Unsatisfiable) and some in pink.

* Edges: Arrows indicating the flow of information.

* Labels: x2, ~x2, x8, x6 are placed on or near the nodes and edges.

* Annotation: "Lookahead: LA(A) < LA(B)" and "In-node Pipeline" are present.

* **Intra-REASON pipeline (symbolic CDCL execution):**

* Modules (Rows): Broadcast, Reduction, L2/DMA, PE Activity, BCP FIFO, Control, Watched Literals.

* Cycles (Columns): T1-T4, T5, T6-T9, T10, T11, T15, T16, T17-T19, T22, T23.

* Side Label: "Multiple parallelable CDCLs" written vertically.

### Detailed Analysis

**1. GPU-REASON Pipeline:**

* The pipeline alternates between GPU (Neuro) and REASON (Symbolic) tasks.

* The "Time" axis indicates the sequential flow of these tasks.

**2. DPLL-lookahead CDCL:**

* A node labeled "A" has an incoming edge labeled "x8" and outgoing edges labeled "x2" and "~x2".

* A node labeled "B" has an incoming edge labeled "x6" and an outgoing edge labeled "~x2".

* Grey nodes are labeled as "Unsatisfiable".

* The "Lookahead: LA(A) < LA(B)" annotation suggests a comparison of lookahead values between nodes A and B.

* The "In-node Pipeline" annotation indicates a process within a node.

**3. Intra-REASON Pipeline (symbolic CDCL execution):**

The table describes the operations performed in each module during different cycles.

* **Broadcast:**

* T1-T4: Broadcast x1

* T5: x1 arrives

* T10: Broadcast x2

* T11: Broadcast x12

* T15: x2 arrives

* T16: x12 arrives

* T17-T19: Broadcast x99

* T22: x99 arrives

* **Reduction:**

* T6-T9: x2=1 propagate then x3=0

* T10: x3 arrives

* T17-T19: Conflict propagate

* **L2/DMA:**

* T15: DMA activated

* T16: DMA activated

* T17-T19: DMA activated

* T22: DMA activated

* T23: Stop DMA

* **PE Activity:**

* T6-T9: Implication x2=1, x3=0

* T17-T19: None

* T22: Conflicts

* **BCP FIFO:**

* T1-T4: \[x12=0, x99=1]

* T5: \[x12=0, x99=1]

* T6-T9: \[x12=0, x99=1]

* T10: \[x12=0, x99=1]

* T11: \[x99=1, x3=0]

* T15: \[x99=1, x3=0]

* T16: \[x3=0]

* T17-T19: \[x3=0]

* T22: \[x3=0]

* T23: \[NULL]

* **Control:**

* T1-T4: Decide x1=0

* T11: Push x3, Pop x12

* T16: Pop x99

* T23: FIFO Flush

* **Watched Literals:**

* T5: No miss detected

* T15: No miss detected

* T16: Miss detected

* T22: conflicts!

### Key Observations

* The GPU-REASON pipeline alternates between GPU-based (Neuro) and REASON-based (Symbolic) processing.

* The DPLL-lookahead CDCL diagram shows a decision tree structure with nodes representing variable assignments and edges representing implications.

* The Intra-REASON pipeline table details the operations performed in different modules across various cycles, showing the flow of data and control signals.

* The BCP FIFO module shows the state of variables x12, x99, and x3 across different cycles.

* The Watched Literals module detects misses and conflicts during the process.

### Interpretation

The diagram illustrates a complex system integrating GPU and REASON processing for solving constraint satisfaction problems using a DPLL-lookahead CDCL approach. The Intra-REASON pipeline provides a detailed view of the symbolic CDCL execution, showing how different modules contribute to the overall solving process. The data suggests a highly parallelizable architecture, as indicated by the "Multiple parallelable CDCLs" label. The pipeline stages and module operations are carefully orchestrated to efficiently propagate constraints, detect conflicts, and make decisions to find a solution. The DPLL-lookahead CDCL structure helps guide the search process by evaluating the potential impact of variable assignments before making a decision.