## Block Diagram: Data-Steering and Multiply-Accumulate Hardware Unit

### Overview

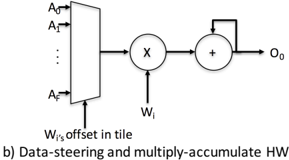

The image is a technical block diagram illustrating a hardware component for data-steering and performing a multiply-accumulate (MAC) operation. It depicts the flow of data from multiple inputs through an offset selection block, into a multiplier, and then into an accumulator (adder with feedback), producing a single output. The diagram is labeled as part "b)" of a larger figure.

### Components/Axes

The diagram consists of the following components, arranged from left to right to indicate data flow:

1. **Input Lines (Left Side):** A set of eight parallel input lines, labeled vertically from top to bottom as:

* `A₀`

* `A₁`

* `A₂`

* `⋮` (ellipsis indicating continuation)

* `A₆`

* `A₇`

These lines feed into a rectangular block.

2. **Data-Steering Block (Left-Center):** A rectangular block receives the eight `A` inputs. It is labeled below with the text: `W₁₅ offset in tile`. This suggests the block selects or offsets data based on a weight parameter (`W₁₅`) within a specific memory or computational tile.

3. **Multiplier (Center):** A circle containing an "X" symbol, representing a multiplication unit. It has two inputs:

* The output from the Data-Steering Block (entering from the left).

* A separate weight input labeled `Wᵢ` (entering from the bottom).

4. **Accumulator / Adder (Center-Right):** A circle containing a "+" symbol, representing an addition unit. It has two inputs:

* The output from the Multiplier (entering from the left).

* A feedback loop from its own output (entering from the top), creating an accumulation function.

5. **Output (Right Side):** A single output line labeled `O₀` emerges from the right side of the Adder.

6. **Caption (Bottom):** Text below the diagram reads: `b) Data-steering and multiply-accumulate HW`.

### Detailed Analysis

* **Data Flow Path:** The primary data path is linear: `A₀-A₇` → `[W₁₅ offset in tile]` → `(X)` with `Wᵢ` → `(+)` with feedback → `O₀`.

* **Component Functions:**

* The **Data-Steering Block** acts as a multiplexer or address offset unit, selecting one of the `A` inputs or applying an offset based on `W₁₅`.

* The **Multiplier** computes the product of the steered data and the weight `Wᵢ`.

* The **Adder with Feedback** implements the "accumulate" part of MAC. It adds the product from the multiplier to its own previous output, effectively summing a series of products over time. The output `O₀` is the running sum.

* **Spatial Grounding:** The legend/labels are placed directly adjacent to their corresponding components. Input labels (`A₀`-`A₇`) are to the left of their lines. The `W₁₅` label is centered below its block. The `Wᵢ` label is below the multiplier. The output label `O₀` is to the right of the output line. The caption is centered below the entire diagram.

### Key Observations

1. **Single Output, Multiple Inputs:** The unit processes eight parallel data inputs (`A₀`-`A₇`) but produces a single accumulated output (`O₀`), indicating it is likely a fundamental processing element within a larger array.

2. **Parameterized Operation:** The operation is controlled by two distinct weight/parameter inputs: `W₁₅` (for data selection/offset) and `Wᵢ` (for multiplication). This suggests programmable or configurable behavior.

3. **Accumulation Loop:** The feedback loop on the adder is a critical feature, defining this as a sequential circuit that maintains state (the accumulated sum) rather than a purely combinational one.

4. **Hierarchical Label:** The prefix "b)" implies this diagram is one part of a multi-part figure (e.g., Figure 1b), describing a specific sub-component of a larger system.

### Interpretation

This diagram represents a fundamental computational unit common in digital signal processing (DSP) and neural network accelerator hardware. The "multiply-accumulate" (MAC) operation is the core of convolution and matrix multiplication algorithms.

* **What it demonstrates:** The unit is designed for efficient, pipelined computation. The "data-steering" block likely handles weight stationary or output stationary dataflows, fetching the correct input activation (`A`) from a local tile of memory based on an offset (`W₁₅`). This product with a weight (`Wᵢ`) is then added to a running sum (`O₀`).

* **Relationships:** The components are chained to form a data pipeline. The steering block decouples input memory access from computation. The multiplier and accumulator form the core MAC engine. The feedback loop enables the summation of many products, which is essential for computing dot products.

* **Contextual Inference:** Given the labels (`W` for weights, `A` for activations), this is almost certainly a building block for a neural network inference or training accelerator. The "tile" reference points to a memory hierarchy designed for data reuse, a key optimization in such hardware. The unit would be replicated many times in a parallel array to perform large matrix operations.