## Code Analysis and Summary

### Overview

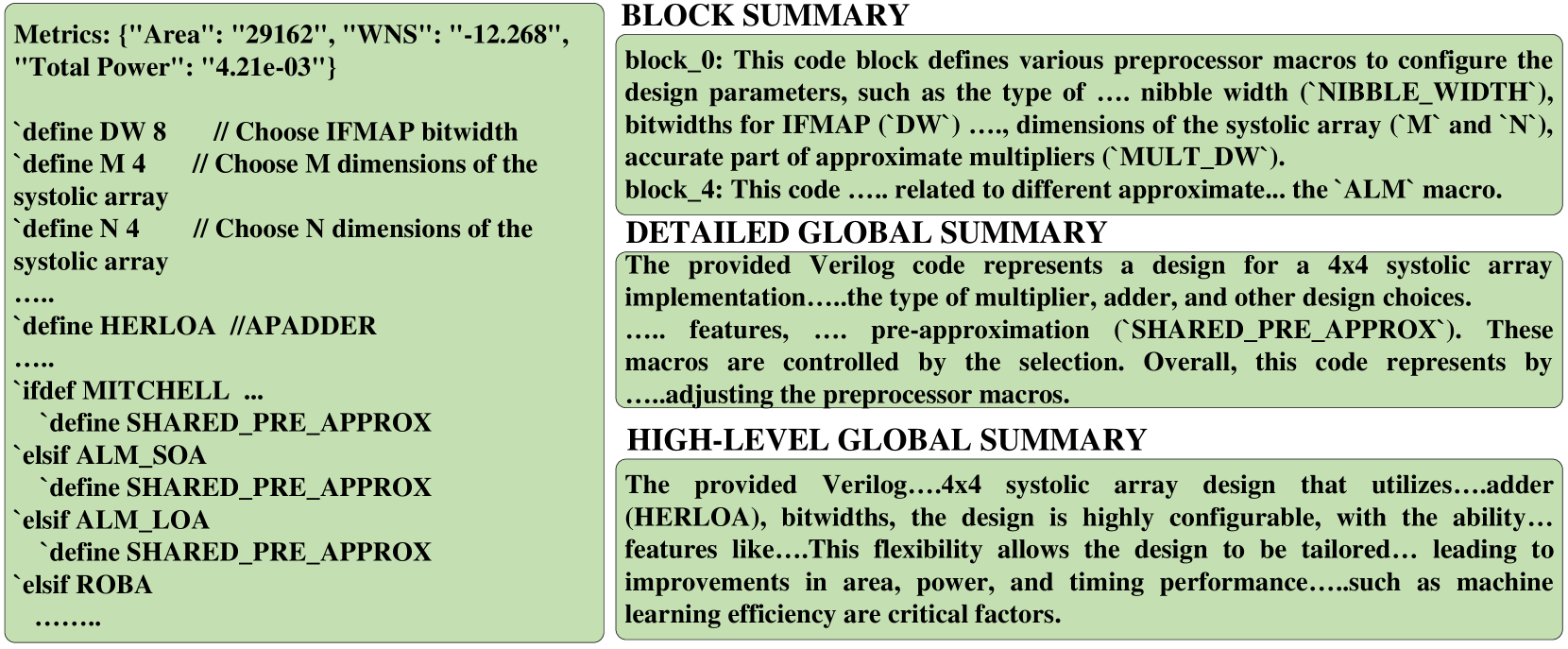

The image presents a code snippet and summaries related to a Verilog design for a 4x4 systolic array. It includes metrics, preprocessor definitions, and block summaries at different levels of detail.

### Components/Axes

* **Metrics:** A dictionary containing "Area", "WNS", and "Total Power".

* **Preprocessor Definitions:** A series of `define` and `ifdef` statements that configure design parameters.

* **Block Summary:** A brief description of the functionality of specific code blocks.

* **Detailed Global Summary:** A more in-depth explanation of the Verilog code's purpose and features.

* **High-Level Global Summary:** A concise overview of the design's capabilities and benefits.

### Detailed Analysis or ### Content Details

**Metrics:**

* Area: 29162

* WNS (Worst Negative Slack): -12.268

* Total Power: 4.21e-03

**Preprocessor Definitions:**

* `define DW 8`: Chooses IFMAP bitwidth.

* `define M 4`: Chooses M dimensions of the systolic array.

* `define N 4`: Chooses N dimensions of the systolic array.

* `define HERLOA //APADDER`

* `ifdef MITCHELL`:

* `define SHARED_PRE_APPROX`

* `elsif ALM_SOA`:

* `define SHARED_PRE_APPROX`

* `elsif ALM_LOA`:

* `define SHARED_PRE_APPROX`

* `elsif ROBA`:

* (Further definitions are truncated in the image)

**Block Summary:**

* block_0: Defines preprocessor macros to configure design parameters like nibble width (`NIBBLE_WIDTH`), IFMAP bitwidths (`DW`), systolic array dimensions (`M` and `N`), and approximate multipliers (`MULT_DW`).

* block_4: Related to different approximate methods, specifically the `ALM` macro.

**Detailed Global Summary:**

* The Verilog code represents a 4x4 systolic array implementation.

* It involves choices for multipliers, adders, and other design elements.

* Features include pre-approximation (`SHARED_PRE_APPROX`), controlled by macro selection.

* The code allows for adjusting preprocessor macros.

**High-Level Global Summary:**

* The Verilog code is for a 4x4 systolic array design using an adder (HERLOA) and configurable bitwidths.

* The design is highly configurable, allowing tailoring for improvements in area, power, and timing performance.

* This is beneficial for applications like machine learning.

### Key Observations

* The code uses preprocessor macros extensively for configuration.

* The design is focused on a 4x4 systolic array architecture.

* Approximation techniques are used, likely for optimization purposes.

* The design aims for improvements in area, power, and timing performance, which are crucial for machine learning applications.

### Interpretation

The image provides a snapshot of a configurable Verilog design for a systolic array. The preprocessor definitions allow for customization of various parameters, such as bitwidths and array dimensions. The summaries highlight the design's focus on optimization and its suitability for machine learning applications. The metrics provide a quantitative assessment of the design's performance in terms of area, timing (WNS), and power consumption. The use of conditional compilation (`ifdef`, `elsif`) suggests that different approximation techniques or design choices can be selected based on specific requirements or constraints.