\n

## Diagram: DRAM Rank Security Mechanism

### Overview

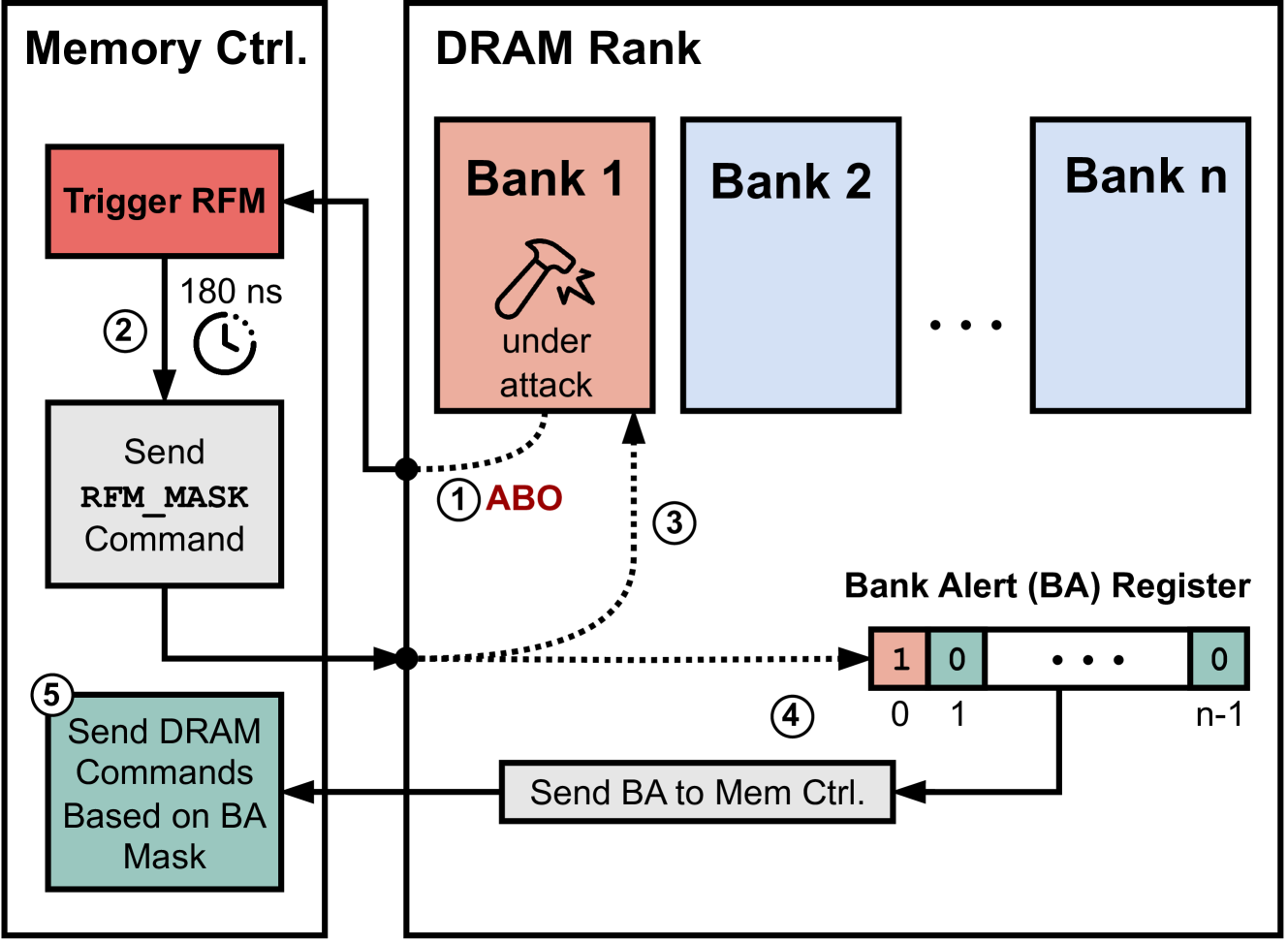

This diagram illustrates a security mechanism for DRAM (Dynamic Random Access Memory) ranks, specifically addressing a "Rowhammer" attack scenario. It depicts the interaction between a Memory Controller and a DRAM Rank, highlighting how a Bank Alert (BA) register is used to mask commands during an attack. The diagram shows a sequence of events triggered by a Rowhammer attack on a specific bank within the DRAM rank.

### Components/Axes

The diagram consists of three main sections:

1. **Memory Ctrl.** (Memory Controller): Located on the left side, this section represents the control logic.

2. **DRAM Rank:** Occupies the central portion, showing multiple banks within the DRAM.

3. **Bank Alert (BA) Register:** Positioned at the bottom, this register stores alert flags for each bank.

Key labels and annotations:

* "Memory Ctrl."

* "DRAM Rank"

* "Bank 1", "Bank 2", "Bank n"

* "under attack" (within Bank 1)

* "Bank Alert (BA) Register"

* "Trigger RFM"

* "180 ns" (with a clock icon)

* "Send RFM_MASK Command"

* "Send BA to Mem Ctrl."

* "Send DRAM Commands Based on BA Mask"

* "ABO" (Alert Bank Output)

* Numbered arrows (1-5) indicating the sequence of events.

* Binary values "0" and "1" within the BA Register, representing bank alert status.

### Detailed Analysis / Content Details

The diagram illustrates a five-step process:

1. **ABO (Alert Bank Output):** When Bank 1 is "under attack", it generates an ABO signal (represented by a dotted arrow).

2. **Trigger RFM:** The Memory Controller receives the ABO signal and triggers an RFM (Rowhammer Fault Mechanism) detection process, with a delay of approximately 180 nanoseconds.

3. **Send RFM_MASK Command:** After the delay, the Memory Controller sends an RFM_MASK command to the DRAM Rank.

4. **Send BA to Mem Ctrl.:** The DRAM Rank sends the Bank Alert (BA) information to the Memory Controller. The BA Register shows that Bank 1 is flagged with a "1", indicating an alert, while all other banks (up to 'n') are flagged with "0", indicating no alert. The register contains 'n' bits, one for each bank.

5. **Send DRAM Commands Based on BA Mask:** The Memory Controller uses the BA mask to selectively send DRAM commands. Commands to the alerted bank (Bank 1) are likely masked or modified to prevent the Rowhammer attack from succeeding.

The dotted lines represent signal flow, while solid lines represent command/data flow. The diagram shows a clear separation between the control logic (Memory Controller) and the memory itself (DRAM Rank).

### Key Observations

* The diagram focuses on a single bank ("Bank 1") being targeted by a Rowhammer attack.

* The BA Register is crucial for identifying and isolating the affected bank.

* The 180 ns delay suggests a timing window for RFM detection.

* The use of a mask implies that the Memory Controller can selectively disable or modify commands to the affected bank.

* The diagram does not specify the exact mechanism for detecting the Rowhammer attack (RFM).

### Interpretation

This diagram demonstrates a hardware-level mitigation strategy for Rowhammer attacks. The core idea is to detect when a bank is being subjected to a potentially harmful sequence of operations (Rowhammer) and then use a Bank Alert mechanism to prevent further damage. The Memory Controller acts as the central authority, receiving alerts from the DRAM Rank and then adjusting its command schedule accordingly.

The BA Register provides a simple but effective way to track the status of each bank. The 180 ns delay likely represents the time required to detect the attack and prepare the RFM_MASK command. The diagram suggests that the system is designed to be proactive, attempting to prevent the attack from succeeding rather than simply reacting to it after it has occurred.

The diagram does not provide details on the specific algorithms or thresholds used for RFM detection, nor does it specify how the RFM_MASK command is implemented. However, it clearly illustrates the overall architecture and flow of the security mechanism. The use of "Bank n" suggests the system is scalable to handle DRAM ranks with a variable number of banks.