\n

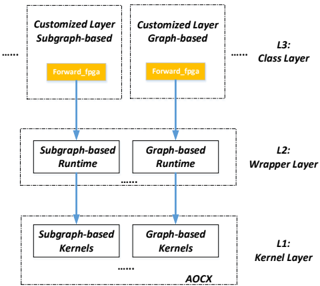

## Diagram: AOCX Layer Architecture

### Overview

The image depicts a layered architecture diagram for a system named "AOCX". It illustrates the flow of data and processing through three layers: L1 (Kernel Layer), L2 (Wrapper Layer), and L3 (Class Layer). Each layer contains two parallel processing paths: one "Subgraph-based" and one "Graph-based". The diagram emphasizes the interaction between these paths at each layer.

### Components/Axes

The diagram is structured into three main layers, labeled on the right side:

* **L3: Class Layer**

* **L2: Wrapper Layer**

* **L1: Kernel Layer**

Within each layer, there are two blocks:

* **Subgraph-based**

* **Graph-based**

Arrows indicate the flow of data from the top layers (L3) down to the bottom layer (L1). Each block in the Class Layer contains the text "Forward_fpga". The bottom layer is labeled "AOCX".

### Detailed Analysis or Content Details

The diagram shows a parallel processing structure.

* **L3 (Class Layer):** Contains two blocks, positioned horizontally.

* Left Block: "Customized Layer Subgraph-based" with "Forward_fpga" inside.

* Right Block: "Customized Layer Graph-based" with "Forward_fpga" inside.

* Dotted arrows originate from both blocks, pointing downwards.

* **L2 (Wrapper Layer):** Contains two blocks, positioned horizontally, directly below the L3 blocks.

* Left Block: "Subgraph-based Runtime"

* Right Block: "Graph-based Runtime"

* Solid arrows originate from the corresponding blocks in L3 and point downwards to the L2 blocks.

* **L1 (Kernel Layer):** Contains two blocks, positioned horizontally, directly below the L2 blocks.

* Left Block: "Subgraph-based Kernels"

* Right Block: "Graph-based Kernels"

* Solid arrows originate from the corresponding blocks in L2 and point downwards to the L1 blocks.

* The entire L1 layer is contained within a rectangular box labeled "AOCX".

The arrows indicate a unidirectional flow of data from the Class Layer (L3) through the Wrapper Layer (L2) to the Kernel Layer (L1). The "Forward_fpga" text suggests a forward pass operation implemented on an FPGA.

### Key Observations

The diagram highlights a dual-path architecture, with both subgraph-based and graph-based processing occurring in parallel at each layer. The "Forward_fpga" label suggests that the forward pass is optimized for FPGA implementation. The AOCX label at the bottom indicates that the entire system is encapsulated within this framework.

### Interpretation

This diagram likely represents the architecture of a hardware acceleration system, specifically designed for deep learning or graph processing. The separation into layers (Class, Wrapper, Kernel) suggests a modular design, where each layer performs a specific function. The parallel subgraph-based and graph-based paths indicate that the system can leverage different processing strategies simultaneously, potentially improving performance and flexibility. The "Forward_fpga" label strongly suggests that the system is intended to be deployed on an FPGA, taking advantage of its parallel processing capabilities. The AOCX label likely refers to a specific hardware or software framework used to manage and optimize the system. The diagram demonstrates a clear flow of data from a high-level customized layer down to the low-level kernel implementation, optimized for FPGA execution.